## MARC4 – 4-bit Microcontroller

The M48C260 is a member of the TEMIC family of 4-bit single chip microcontrollers. It is the user programmable version of the M44C260. It contains EEPROM program memory, RAM, EEPROM data memory, parallel I/O ports, 1 timer with watchdog function,  $2 \times 8/16$ -bit multifunction timer/counter and the on-chip clock generation.

#### **Features**

- 4-bit HARVARD architecture

- 1 µs instruction cycle

- $4K \times 8$ -bit application EEPROM program memory

- 256 × 4-bit RAM

- 16 × 8-bit EEPROM

- 16 bidirectional I/O's

- 8 hard and software interrupt levels

- 2 × 8-bit multifunction timer/counter

- Interval timer with watchdog

- 32 kHz on-chip oscillator

Rev. A1: 19.06.1995

## **Benefits**

- Low power consumption

- Power down mode  $< 1 \mu A$

- 2.4 to 6.2 V supply voltage

- Self test functions

- High level programming language in qFORTH

- User programmable with the application program

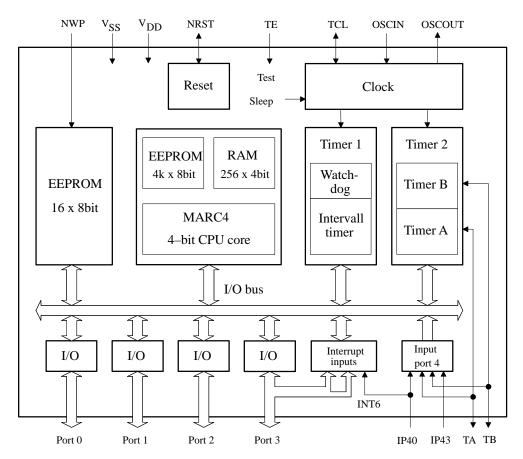

Figure 1. Block diagram

94 9038

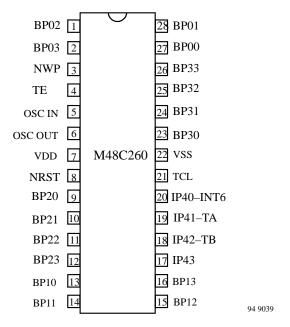

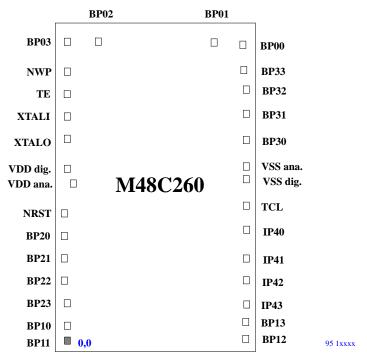

Figure 2. Pin connections for SSO28-FN

Table 1. Pin description

| Name        | Function                                                                                                                                                                                                    |  |  |  |  |  |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| $V_{DD}$    | Power supply voltage +2.4 to +6.2 V                                                                                                                                                                         |  |  |  |  |  |

| $V_{SS}$    | Circuit ground                                                                                                                                                                                              |  |  |  |  |  |

| BP00 – BP03 | 4 bidirectional I/O lines of port 0 *                                                                                                                                                                       |  |  |  |  |  |

| BP10 – BP13 | 4 bidirectional I/O lines of port 1 *                                                                                                                                                                       |  |  |  |  |  |

| BP20 – BP23 | 4 bidirectional I/O lines of port 2 *                                                                                                                                                                       |  |  |  |  |  |

| BP30 – BP33 | 4 bidirectional I/O lines of port 3 with alternate interrupt function. A negative transition on BP30/BP31 requests an INT2-, and on BP32/BP33 an INT3-interrupt if the corresponding interrupt-mask is set. |  |  |  |  |  |

| IP40-INT6   | Input port 40 line/interrupt 6 input * A negative transition on this input requests an INT6 interrupt if the IM6 mask bit is set.                                                                           |  |  |  |  |  |

| IP41-TA     | Timer/counter I/O/Input port 41 line * This line can be used as programmable I/O of counter A or as port 41 input.                                                                                          |  |  |  |  |  |

| IP42-TB     | Timer/counter I/O/input port 42 line * This line can be used as programmable I/O of counter B or as port 42 input.                                                                                          |  |  |  |  |  |

| IP43        | Input port 43 line *)                                                                                                                                                                                       |  |  |  |  |  |

| NWP         | EEPROM write protect input, a logic low on this input protects EEPROM rows 12 to 15.                                                                                                                        |  |  |  |  |  |

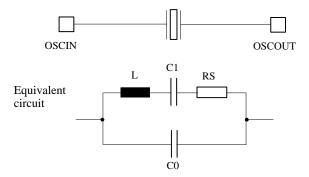

| OSCIN       | Oscillator input (32-kHz crystal).                                                                                                                                                                          |  |  |  |  |  |

| OSCOUT      | Oscillator output (32-kHz crystal).                                                                                                                                                                         |  |  |  |  |  |

| NRST        | Reset input/output, a logic low on this pin resets the device. An internal watchdog reset is indicated by a low level on this pin.                                                                          |  |  |  |  |  |

| TCL         | External system clock I/O. This pin can be used as input to provide the C with an external clock or as output of the internal system clock.                                                                 |  |  |  |  |  |

| TE          | Testmode input. This input is used to control the test modes and the function of the TCL pin.                                                                                                               |  |  |  |  |  |

<sup>\*)</sup> The I/O ports have CMOS output buffers. As input they are available with pull-up or pull-down resistors. Please see the order information.

## M48C260

# TEMIC

TELEFUNKEN Semiconductors

## **Contents**

| 1 | MARC4 Architecture |             |                                           |  |  |  |  |  |

|---|--------------------|-------------|-------------------------------------------|--|--|--|--|--|

|   | 1.1                | General D   | escription                                |  |  |  |  |  |

|   | 1.2                | Componer    | nts of MARC4 Core                         |  |  |  |  |  |

|   |                    | 1.2.1       | Program Memory (ROM)                      |  |  |  |  |  |

|   |                    | 1.2.2       | Data Memory (RAM)                         |  |  |  |  |  |

|   |                    | 1.2.3       | Registers                                 |  |  |  |  |  |

|   |                    | 1.2.4       | ALU                                       |  |  |  |  |  |

|   |                    | 1.2.5       | Instruction Cycles                        |  |  |  |  |  |

|   |                    | 1.2.6       | I/O Bus                                   |  |  |  |  |  |

|   |                    | 1.2.7       | Interrupt Structure                       |  |  |  |  |  |

|   |                    |             | Software Interrupts                       |  |  |  |  |  |

|   |                    |             | Hardware Interrupts                       |  |  |  |  |  |

|   | 1.3                | Reset       |                                           |  |  |  |  |  |

|   | 1.4                | Clock Gen   | neration                                  |  |  |  |  |  |

|   |                    | 1.4.1       | Clock Status/Control Register (CSC)       |  |  |  |  |  |

|   |                    | 1.4.2       | TCL Signal                                |  |  |  |  |  |

|   | 1.5                | Power Do    | wn Modes                                  |  |  |  |  |  |

| 2 | Donin              | hanal Madul | les                                       |  |  |  |  |  |

| • | 2.1                |             |                                           |  |  |  |  |  |

|   | 2.1                | 2.1.1       | g Peripherals                             |  |  |  |  |  |

|   |                    | 2.1.1       | Bidirectional Ports                       |  |  |  |  |  |

|   |                    | 2.1.2       | External Interrupt Inputs                 |  |  |  |  |  |

|   | 2.2                |             | External interrupt inputs                 |  |  |  |  |  |

|   | 2.2                | 2.2.1       | T1C – Timer 1 Control Register            |  |  |  |  |  |

|   |                    | 2.2.2       | WDC – Watchdog Control Register           |  |  |  |  |  |

|   | 2.3                |             |                                           |  |  |  |  |  |

|   | 2.3                | 2.3.1       | Timer 2 Status/Control Register (T2SC)    |  |  |  |  |  |

|   |                    | 2.3.2       | Timer 2 Subport (T2SUB)                   |  |  |  |  |  |

|   |                    | 2.3.3       | Timer 2 Reload Register                   |  |  |  |  |  |

|   |                    | 2.3.4       | Timer 2 Capture Register                  |  |  |  |  |  |

|   |                    | 2.3.5       | Timer A Mode Register 1 (TAM1)            |  |  |  |  |  |

|   |                    | 2.3.6       | Timer A Mode Register 2 (TAM2)            |  |  |  |  |  |

|   |                    | 2.3.7       | Timer B Mode Register 1 (TBM1)            |  |  |  |  |  |

|   |                    | 2.3.8       | Timer B Mode Register 2 (TBM2)            |  |  |  |  |  |

|   |                    | 2.3.9       | Timer 2 Prescaler Control Register (T2PC) |  |  |  |  |  |

|   |                    | 2.3.10      | Timer 2 Interrupt Control Register (T2IC) |  |  |  |  |  |

|   |                    | 2.3.11      | Timer I/O (TA/TB)                         |  |  |  |  |  |

|   | 2.4                | EEPROM      |                                           |  |  |  |  |  |

|   |                    | 2.4.1       | EEPROM Mode/Status Register (EMS)         |  |  |  |  |  |

## M48C260

**TELEFUNKEN Semiconductors**

## **Contents (continued)**

| 3 | Emul  | ation      |                                      | 30 |

|---|-------|------------|--------------------------------------|----|

|   | 3.1   | MARC       | 4 Instruction Set                    | 30 |

|   |       | 3.1.1      | MARC4 Instruction Set Overview       | 31 |

|   |       | 3.1.2      | qFORTH Language Overview             | 32 |

|   | 3.2   | The qF0    | ORTH language -Quick Reference Guide | 33 |

|   |       | 3.2.1      | Arithmetic/Logical                   | 33 |

|   |       | 3.2.2      | Comparisons                          | 33 |

|   |       | 3.2.3      | Control Structures                   | 34 |

|   |       | 3.2.4      | Stack Operations                     | 34 |

|   |       | 3.2.5      | Memory Operations                    | 35 |

|   |       | 3.2.6      | Predefined Structures                | 36 |

|   |       | 3.2.7      | Assembler Mnemonics                  | 36 |

| 4 | Elect | rical Char | acteristics                          | 38 |

|   | 4.1   | Absolut    | e Maximum Ratings                    | 38 |

|   | 4.2   | DC Ope     | erating Characteristics              | 38 |

|   | 4.3   | AC Cha     | racteristics                         | 40 |

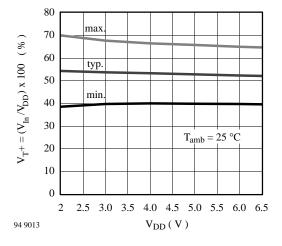

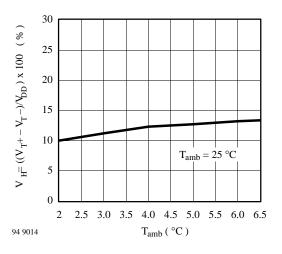

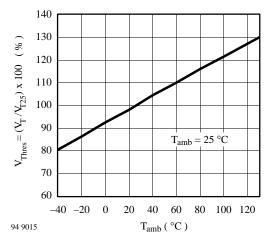

|   | 4.4   | Schmitt    | -Trigger Inputs                      | 45 |

| 5 | Pad I | Layout     |                                      | 46 |

| 6 | Orde  | ring Infor | mation                               | 47 |

#### 1 **MARC4** Architecture

#### 1.1 **General Description**

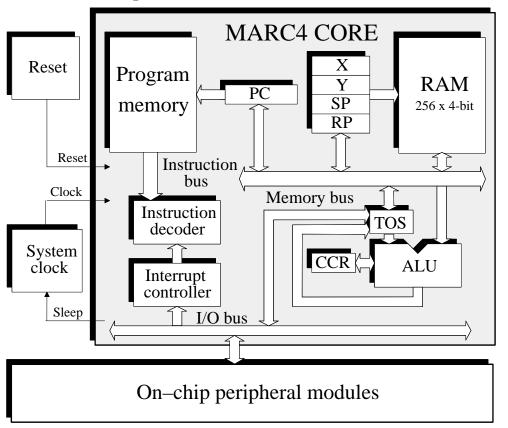

Figure 3. MARC4 core

The MARC4 microcontroller consists of an advanced stack based 4-bit CPU core and on-chip peripherals. The CPU is based on the HARVARD architecture with physically separate program memory (EEPROM) and data memory (RAM). Three independent buses, the instruction bus, the memory bus and the I/O bus are used for parallel communication between ROM, RAM and peripherals. This enhances program execution speed by allowing both instruction prefetching, and a simultaneous communication to the on-chip peripheral circuitry. The integrated powerful interrupt controller with eight prioritized interrupt levels, supports fast processing of hardware events.

The MARC4 is designed for the high level programming language qFORTH. The core contains both FORTH stacks, expression stack and return stack. This architecture allows high level language programming without any loss in efficiency or code density.

#### 1.2 **Components of MARC4 Core**

The core contains program memory, RAM, ALU, program counter, RAM address register, instruction decoder and interrupt controller. The following sections describe each of this parts.

94 8973

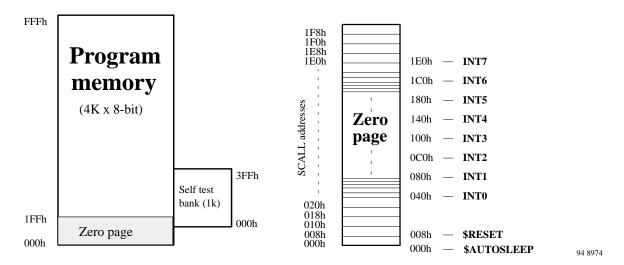

#### 1.2.1 **Program Memory (EEPROM)**

The program memory (EEPROM) is programmed with the application program by the customer using a special programming device (see chapter "Progamming the EEPROM Program Memory"). The ROM is addressed by a 12-bit wide program counter, thus limiting the program size to a maximum of 4 Kbytes. An additional 1 Kbyte ROM is available for test software only..

The EEPROM starts with a 512 byte segment (zero page) which contains predefined start addresses for interrupt service routines and special subroutines accessible with single byte instructions (SCALL). The corresponding memory map is shown in figure 4.

Look-up tables of constants can also be held in EEPROM and are accessed via the MARC4's built-in TABLE instruction.

Figure 4. Program memory map

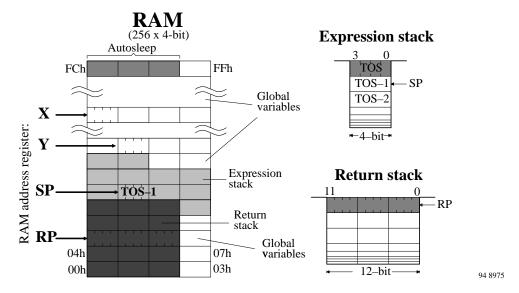

## 1.2.2 Data Memory (RAM)

The MARC4 contains 256 x 4-bit wide static random access memory (RAM). It is used for the expression stack, the return stack and data memory for variables and arrays. The RAM is addressed by any of the four 8-bit wide RAM address registers SP, RP, X and Y.

### Expression Stack

The 4-bit wide expression stack is addressed with the expression stack pointer (SP). All arithmetic, I/O and memory reference operations take their operands from, and return their result to the expression stack. The MARC4 performs the operations with the top of stack items (TOS and TOS-1). The TOS register contains the top element of the expression stack and works like an

accumulator. This stack is also used for passing parameters between subroutines, and as a scratchpad area for temporary storage of data.

#### • Return Stack

The 12-bit wide return stack is addressed by the return stack pointer (RP). It is used for storing return addresses of subroutines, interrupt routines and for keeping loop index counts. The return stack can also be used as a temporary storage area.

The MARC4 instruction set supports the exchange of data between the top elements of the expression stack and the return stack. The two stacks within the RAM have a user definable location and maximum depth.

Figure 5. RAM map

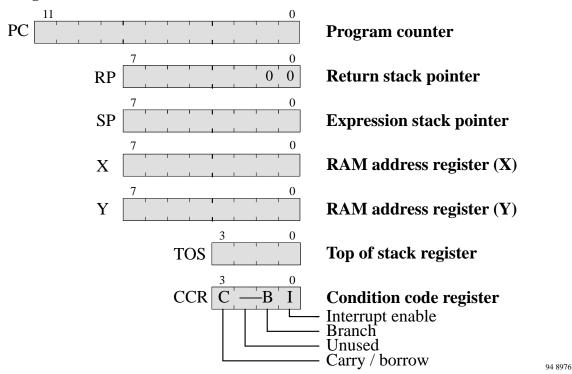

## 1.2.3 Registers

Figure 6. Programming model

The MARC4 controller has six programmable registers and one condition code register. They are shown in the following programming model.

#### • Program Counter (PC)

The program counter (PC) is a 12-bit register that contains the address of the next instruction to be fetched from the program memory. Instructions currently being executed are decoded in the instruction decoder to determine the internal micro operations. For linear code (no calls or branches) the program counter is incremented with every instruction cycle. If a branch-, call-, return-instruction or an interrupt is executed the program counter is loaded with a new address. The program counter is also used with the TABLE instruction to fetch 8-bit wide ROM constants.

#### RAM address register

The RAM is addressed with the four 8-bit wide RAM address registers: SP, RP, X and Y. These registers allow access to any of the 256 RAM nibbles.

#### Expression Stack Pointer (SP)

The stack pointer (SP) contains the address of the next-totop 4-bit item (TOS-1) of the expression stack. The pointer is automatically pre-incremented if a nibble is moved onto the stack or post-decremented if a nibble is removed from the stack. Every post-decrement operation moves the item (TOS-1) to the TOS register before the SP is decremented. After a reset the stack pointer has to be initialized with ">SP \$xx" to allocate the start address of the expression stack area.

#### • Return Stack Pointer (RP)

The return stack pointer points to the top element of the 12-bit wide return stack. The pointer automatically preincrements if an element is moved onto the stack or it post-decrements if an element is removed from the stack. The return stack pointer increments and decrements in steps of 4. This means that every time a 12-bit element is stacked, a 4-bit RAM location are left unwritten. These location are used by the qFORTH compiler to allocate 4-bit variables. After a reset the return stack pointer has to be initialized with ">RP FCh".

#### • RAM Address Register (X and Y)

The X and Y registers are used to address any 4-bit item in the RAM. A fetch operation moves the addressed nibble onto the TOS. A store operation moves the TOS to the addressed RAM location. Using either the pre-increment or post-decrement addressing mode arrays in the RAM can be compared, filled or moved.

#### • Top Of Stack (TOS)

The top of stack register is the accumulator of the MARC4. All arithmetic/logic, memory reference and I/O operations use this register. The TOS register gets the data from the ALU, the program memory, the RAM or via the I/O bus.

#### • Condition Code Register (CCR)

The 4-bit wide condition code register contains the branch, the carry and the interrupt enable flag. These bits indicates the current state of the CPU. The CCR flags are set or reset by ALU operations. The instructions SET\_BCF, TOG\_BF, CCR! and DI allow a direct manipulation of the condition code register.

#### Carry/Borrow (C)

The carry/borrow flag indicates that borrow or carry out of arithmetic logic unit (ALU) occurred during the last arithmetic operation. During shift and rotate operations this bit is used as a fifth bit. Boolean operations have no affect on the C flag.

#### Branch (B)

The branch flag controls the conditional program branching. When the branch flag was set by one of the previous instructions a conditional branch is taken. This flag is affected by arithmetic, logic, shift, and rotate operations.

#### **Interrupt Enable (I)**

The interrupt enable flag enables or disables the interrupt processing on a global basis. After reset or by executing the DI instruction the interrupt enable flag is reset and all interrupts are disabled. The  $\mu C$  does not process further interrupt requests until the interrupt enable flag is set again by either executing an EI, RTI or SLEEP instruction.

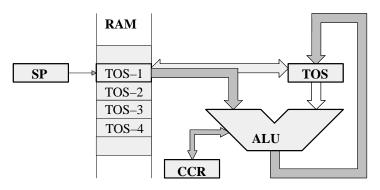

#### 1.2.4 ALU

The 4-bit ALU performs all the arithmetic, logical, shift and rotate operations with the top two elements of the expression stack (TOS and TOS-1) and returns its result to the TOS. The ALU operations affect the carry/borrow and branch flag in the condition code register (CCR).

Figure 7. ALU zero address operations

## 1.2.5 Instruction Cycles

A MARC4 instruction word is one or two byte long and is executed within one or four machine-cycles. A machine-cycle consists of two system clocks (SYSCL). The MARC4 is a zero address machine. Most of the instructions are one byte long and are executed in only one machine-cycle. The CPU has an instruction pipeline, this allows the controller to fetch the next instruction from program memory at the same time as the present instruction is being executed. For more informations see section "MARC4 Instruction Set Overview".

## 1.2.6 I/O Bus

The I/O ports and the registers of the peripheral modules (timer 1, timer 2, EEPROM) are I/O mapped. The communication between the core and the on-chip peripherals takes place via the I/O bus and the associated I/O control bus. These buses are used for different functions: for read and write accesses, for the interrupt generation, to reset peripherals and for the SLEEP mode. With the MARC4 IN-instruction and OUT-instructions the I/O bus allows a direct read or write access to one of the 16 I/O addresses. More about the I/O access to the on-chip peripherals is described in the section "Peripheral modules".

The I/O buses are internal buses and are not accessible by the customer on the final microcontroller device, but they are used as the interface for the MARC4 emulation (see also the section "Emulation").

94 8977

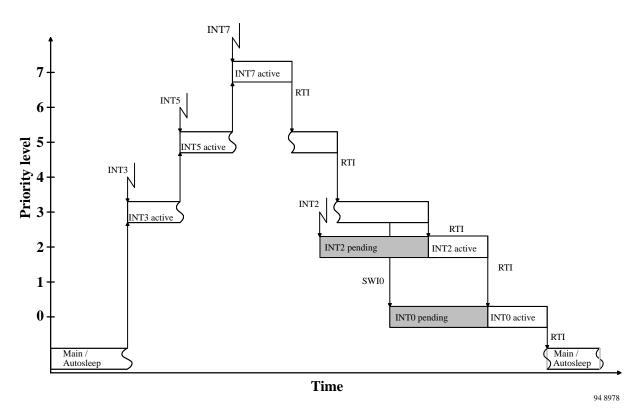

## 1.2.7 Interrupt Structure

The MARC4 can handle interrupts with eight different priority levels. They can be generated from the internal and external interrupt sources or by a software interrupt from the CPU itself. Each interrupt level has a hard-wired priority and an associated vector for the service routine in the ROM (see table 2). The programmer can enable or disable interrupts all together by setting or resetting the interrupt enable flag (I) in the CCR.

#### Interrupt processing

For processing the eight interrupt levels the MARC4 contains an interrupt controller with the 8-bit wide interrupt pending and interrupt active register. The interrupt controller samples all interrupt requests during every non-I/O instruction cycle and latches them in the interrupt pending register. If no higher priority interrupt is present in the interrupt active register it signals the CPU to interrupt the current program execution. If the interrupt enable bit is set the processor enters an interrupt acknowledge cycle. During this cycle a SHORT CALL instruction to the ser-

vice routine is executed and the current PC is saved on the return stack. An interrupt service routine is finished with the RTI instruction. This instruction sets the interrupt enable flag, resets the corresponding bits in the interrupt pending/active register and fetches the return address from the return stack to the program counter. When the interrupt enable flag is reset (interrupts are disabled), the execution of interrupts is inhibited but not the logging of the interrupt requests in the interrupt pending register. The execution of the interrupt will be delayed until the interrupt enable flag is set again. But note that interrupts are lost if an interrupt request occurs during the corresponding bit in the pending register is still set. After the reset (power-on, external or watchdog reset), the interrupt enable flag and the interrupt pending and interrupt active register are reset.

## **Interrupt latency**

The interrupt latency is the time from the falling edge of the interrupt to the interrupt service routine being activated. In the MARC4 this takes between 3 to 5 machine cycles depending on the state of the core.

Figure 8. Interrupt handling

Table 2. Interrupt priority table

| Interrupt | Priority | Vector<br>Address | Interrupt Opcode<br>(Acknowledge) | Function                                                  |

|-----------|----------|-------------------|-----------------------------------|-----------------------------------------------------------|

| INT0      | lowest   | 040h              | C8h (SCALL 040h)                  | Software interrupt (SWI0)                                 |

| INT1      |          | 080h              | D0h (SCALL 080h)                  | EEPROM write ready                                        |

| INT2      |          | 0C0h              | D8h (SCALL 0C0h)                  | External hardware interrupt,<br>neg. edge at BP30 or BP31 |

| INT3      |          | 100h              | E0h (SCALL 100h)                  | External hardware interrupt,<br>neg. edge at BP32 or BP33 |

| INT4      |          | 140h              | E8h (SCALL 140h)                  | Timer 1 interrupt                                         |

| INT5      |          | 180h              | F0h (SCALL 180h)                  | Timer 2 interrupt                                         |

| INT6      |          | 1C0h              | F8h (SCALL 1C0h)                  | External hardware interrupt, neg. edge at IP40 pin        |

| INT7      | highest  | 1E0h              | FCh (SCALL 1E0h)                  | Software interrupt (SWI7)                                 |

## **Software Interrupts**

The programmer can generate interrupts using the software interrupt instruction (SWI) which is supported in qFORTH by predefined macros named SWI0 to SWI7. The software triggered interrupt operates exactly like any hardware triggered interrupt. The SWI instruction takes the top two elements from the expression stack and writes the corresponding bits via the I/O bus to the interrupt

pending register. Thus using the SWI instruction, interrupts can be re-prioritized or lower priority processes scheduled for later execution.

## **Hardware Interrupts**

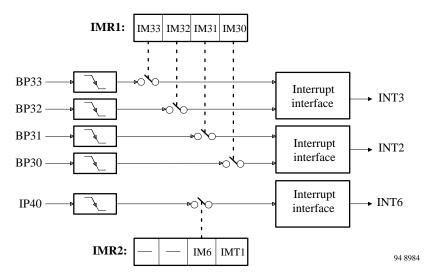

In the M44C260 are eleven hardware interrupt sources with six different levels. Each of these sources can be enabled or disabled separately with an interrupt mask bit in the IMR1 or IMR2 register.

Table 3. Hardware interrupts

| Interrupt                 | Priority | M        | ask  | Interrupt Source               |

|---------------------------|----------|----------|------|--------------------------------|

|                           |          | Register | Bit  |                                |

| EEPROM write ready        | INT1     | EMS      | IMEP | EEPROM end of write cycle      |

| External interrupt        | INT2     | IMR1     | IM30 | Negative edge at BP30          |

| port 3 (BP30 OR BP31)     |          |          | IM31 | Negative edge at BP31          |

| External interrupt        | INT3     | IMR1     | IM32 | Negative edge at BP32          |

| port 3 (BP32 OR BP33)     |          |          | IM33 | Negative edge at BP33          |

| Timer 1 interrupt         | INT4     | IMR2     | IMT1 | Timer 1                        |

| Timer 2 interrupt         | INT5     | T2IC     | IMAS | Timer A end of space/underflow |

|                           |          |          | IMAP | Timer A end of pulse/capture   |

|                           |          |          | IMBS | Timer B end of space/underflow |

|                           |          |          | IMBP | Timer B end of pulse/capture   |

| Ext. interrupt IP40 input | INT6     | IMR2     | IM6  | Negative edge at IP40 input    |

## 1.3 Reset

The reset puts the CPU into a well-defined condition. The reset can be triggered by switching on the supply voltage, by a break-down of the supply voltage, by the watchdog timer or by pulling the NRST pad to low.

After any reset the branch-, carry- and interrupt enable flag in the Condition Code Register (CCR), the interrupt pending register and the interrupt active register are reset.

During the reset-cycle the I/O bus control signals are set to 'reset mode' thereby initializing all on-chip peripherals.

A reset is finished with a short call instruction (opcode C1h) to the program memory address 008h. This activates the initialization routine \$RESET. With that routine the stack pointers, variables in the RAM and the peripheral must be initialized.

## TELEFUNKEN Semiconductors

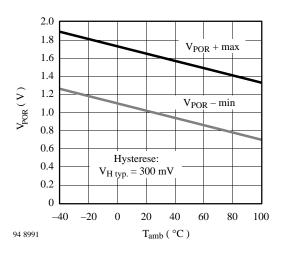

#### Power-on Reset

The power-on reset ensures that the core is activated not before the operating supply voltage has been reached.

A reset is also generated when the supply voltage remains below the operating range for more than 5 ms.

#### **External Reset (NRST)**

An external reset can be triggered with the NRST pin. For the external reset the pin should be low for a minimum of two machine cycles.

#### **Watchdog Timer Reset**

If the watchdog timer function of Timer 1 is enabled a reset is triggered with every watchdog counter overflow. To suppress that the watchdog counter must be reset by an access to the CWD-register (see also Timer 1/watchdog counter).

The power-on reset and watchdog reset are indicated in the same way as an external reset on the NRST pad.

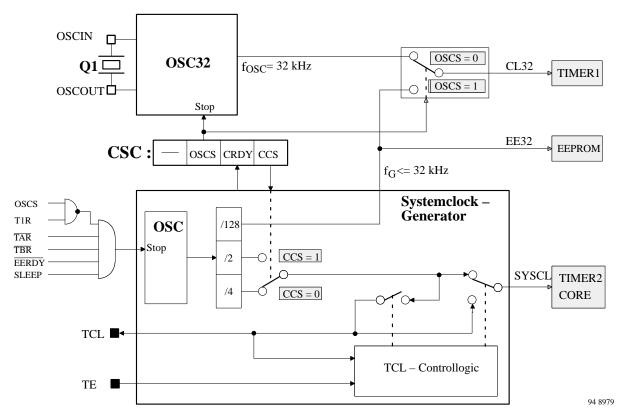

## 1.4 Clock Generation

The M48C260 has two oscillators, one RC oscillator for the system clock generation and an additional 32-kHz crystal oscillator. The system clock generator provides the core and Timer 2 with the clock. The system clock frequency of the M48C260 is programmable for 1 or 2 MHz. The crystal oscillator is used as an exact time base for Timer 1. If no exact timing is required, the controller does not need an external crystal. In this case Timer 1 is provided with the system clock.

The configuration for both oscillators is programmable with the clock status control register (CSC), which is a subport register located in port CSUB. The required configuration has to be initialized after reset in the \$RESET routine. The default setting after a reset is 1 MHz system clock and an active 32-kHz crystal oscillator.

After power-on or a SLEEP instruction the clock generator needs a start-up time until it runs with an exact timing. The CRDY bit in the CSC register indicates the start-up phase.

Figure 9. Clock module

## 1.4.1 Clock Status/Control Register (CSC)

Address: Ch Subaddress: 2h

OSCS Oscillator Stop

When OSCS = 0 the controller is configured to run with the 32-kHz crystal oscillator for Timer 1. When OSCS = 1 the 32-kHz oscillator stops. For  $\mu$ C operation without crystal, this bit must be set after reset. In that case Timer 1 is provided from the internal RC oscillator.

CRDY Clock Ready (status bit)

CRDY = 0 indicates the start-up time of the oscillators.

CRDY = 1 indicates that the clock is ready. The  $\mu$ C runs with an exact timing.

**CCS** Core Clock Select

CCS = 0 selects 1 MHz system clock (SYSCL/TCL) CCS = 1 selects 2 MHz system clock (SYSCL/TCL)

### 1.4.2 TCL Signal

The TCL pin can be used as input to supply the controller with an external clock. For this configuration the TCL pin must be held low for at least 0.5 ms during the reset cycle. The controller is working with clock frequencies up to 2.5 MHz. It is also possible to use the TCL pin as output to supply peripherals with the system clock. In this case the TE pin must be connected to  $V_{DD}$  level and the TCL pin must have a high impedance load.

### 1.5 Power Down Modes

The sleep mode is a shutdown condition which is used to reduce the average system power consumption in applications where the  $\mu C$  is not fully utilized. In this mode the system clock is stopped. The sleep mode is entered with the SLEEP instruction. This instruction sets the interrupt enable bit (I) in the condition code register to enable all interrupts and stops the core. During the sleep mode the peripheral modules remain active and are able to generate interrupts. The  $\mu C$  exits the sleep mode with any interrupt or a reset.

The sleep mode can only be kept when none of the interrupt pending or active register bits are set. The application of the \$AUTOSLEEP routine ensures the correct function of the sleep mode.

The total power consumption is directly proportional to the active time of the  $\mu C$ . For a rough estimation of the expected average system current consumption, the following formula should be used:

$I_{total}(V_{DD}, f_{Osc}) = I_{Sleep} + (I_{DD} * T_{active}/T_{total})$

I<sub>DD</sub> depends on V<sub>DD</sub> and f<sub>Osc</sub>.

#### **Systemclock Generator Stop**

The M48C260 has different power down modes. When the MARC4 core enters the sleep mode and no on-chip peripheral needs a clock signal (SYSCL) the system clock oscillator is stopped. Therefor the programmer should stop timer 1 and timer 2 during the sleep mode if they are not required. If the 32-kHz oscillator is not used it should be stopped. Under this condition the power consumption is extremely low (see following table).

Table 4. Power consumption at different power down modes

| Mode | CPU-<br>Core | TIMER 1 [T1R]<br>TIMER 2 [TAR, TBR]<br>EEPROM [EERDY] | RC Osc. | 32-kHz-<br>Osc.<br>[OSCS] | Power-Consumption [µA] |

|------|--------------|-------------------------------------------------------|---------|---------------------------|------------------------|

| 1    | SLEEP        | T1R=0 AND TAR=0 AND TBR=0 AND EERDY=1                 | STOP    | STOP                      | < 1.0                  |

| 2    | SLEEP        | T1R=X, TAR=0 AND TBR=0 AND EERDY=1                    | STOP    | RUN                       | < 1.0                  |

| 3    | SLEEP        | T1R=1 OR TAR=1 OR TBR=1 OR EERDY=0                    | RUN     | STOP                      | < x                    |

| 4    | SLEEP        | T1R=X, TAR=1 OR TBR=1 OR EERDY=0                      | RUN     | RUN                       | < x                    |

| 5    | RUN          | T1R=X, TAR=X, TBR=X, EERDY=X                          | RUN     | STOP                      | < y                    |

| 6    | RUN          | T1R=X, TAR=X, TBR=X, EERDY=X                          | RUN     | RUN                       | < y                    |

94 8980

## TEMIC

## 2 Peripheral Modules

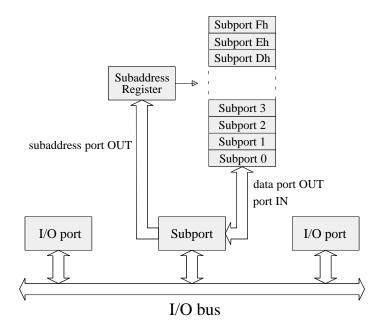

## 2.1 Addressing Peripherals

The access to the peripheral modules (ports, registers) is executed via the I/O bus. The IN- or OUT-instruction allows the direct addressing of 16 I/O ports. For the peripherals with a large number of registers, extended addressing is used. With two I/O operations an extended

I/O port allows the access to 16 subports. The first OUT-instruction writes the subport address to the subaddress register, the second IN- or OUT-instruction reads data from or writes data to the addressed subport.

Table 5. I/O-addressing

| I/O Operation                 | qFORTH Instructions | Description                           |

|-------------------------------|---------------------|---------------------------------------|

| Port 0, 1, 2, 3, 4, T2SC, EMS | S                   |                                       |

| I/O read                      | port IN             | Read data from port                   |

| I/O write                     | data port OUT       | Write data to port                    |

| T2SUB, CSUB                   | •                   |                                       |

| Extended I/O read             | subaddress port OUT | Write subaddress to port              |

|                               | port IN             | Read data from subaddress             |

| Extended I/O write            | subaddress port OUT | Write subaddress to port              |

|                               | data port OUT       | Write data to subaddress              |

| Extended I/O short read       | port IN             | Read data from current subaddress     |

| ESUB                          |                     |                                       |

| Extended I/O read (byte)      | subaddress port OUT | Write subaddress to port              |

|                               | port IN             | Read data high nibble from subaddress |

|                               | port IN             | Read data low nibble from subaddress  |

| Extended I/O write (byte)     | subaddress port OUT | Write subaddress to port              |

|                               | data port OUT       | Write data low nibble to subaddress   |

|                               | data port OUT       | Write data high nibble to subaddress  |

Figure 10. Extended I/O addressing

Table 6. Peripheral addresses

| Addr. | Name   |                                                   |                                     | Fu                             | nction                                              |  |  |  |  |  |  |

|-------|--------|---------------------------------------------------|-------------------------------------|--------------------------------|-----------------------------------------------------|--|--|--|--|--|--|

| 0     | Port 0 | Ridirectional port                                | Bidirectional port                  |                                |                                                     |  |  |  |  |  |  |

| 1     | Port 1 | -                                                 | Bidirectional port                  |                                |                                                     |  |  |  |  |  |  |

| 2     | Port 2 |                                                   | Bidirectional port                  |                                |                                                     |  |  |  |  |  |  |

| 3     | Port 3 | <del>• • • • • • • • • • • • • • • • • • • </del> | Bidirectional port                  |                                |                                                     |  |  |  |  |  |  |

| 4     | Port 4 | nput port                                         |                                     |                                |                                                     |  |  |  |  |  |  |

| 5     |        | iiput port                                        |                                     |                                |                                                     |  |  |  |  |  |  |

| 6     |        |                                                   |                                     |                                |                                                     |  |  |  |  |  |  |

| 7     |        |                                                   |                                     |                                |                                                     |  |  |  |  |  |  |

| 8     | T2SC   |                                                   | Timer 2 status and control register |                                |                                                     |  |  |  |  |  |  |

| 9     | T2SUB  | Subport for timer 2                               | Sub-                                | Name                           | Register                                            |  |  |  |  |  |  |

|       |        |                                                   | address                             |                                |                                                     |  |  |  |  |  |  |

|       |        |                                                   | 0                                   | TARCH                          | Timer 2A space reload/capture register, high nibble |  |  |  |  |  |  |

|       |        |                                                   | 1                                   | TARCL                          | Timer 2A space reload/capture register, low nibble  |  |  |  |  |  |  |

|       |        |                                                   | 2                                   | Timer 2A pulse reload register |                                                     |  |  |  |  |  |  |

|       |        |                                                   | 3                                   | TARH<br>TARL                   | Timer 2A pulse reload register                      |  |  |  |  |  |  |

|       |        |                                                   | 4                                   | TBRCH                          | Timer 2B space reload/capture register, high nibble |  |  |  |  |  |  |

|       |        |                                                   | 5                                   | TBRCL                          | Timer 2B space reload/capture register, low nibble  |  |  |  |  |  |  |

|       |        |                                                   | 6                                   | TBRH                           | Timer 2B pulse reload register                      |  |  |  |  |  |  |

|       |        |                                                   | 7                                   | TBRL                           | Timer 2B pulse reload register                      |  |  |  |  |  |  |

|       |        |                                                   | 8                                   | TAM1                           | Timer 2A mode register 1                            |  |  |  |  |  |  |

|       |        |                                                   | 9                                   | TAM2                           | Timer 2A mode register 2                            |  |  |  |  |  |  |

|       |        |                                                   | A                                   | TBM1                           | Timer 2B mode register 1                            |  |  |  |  |  |  |

|       |        |                                                   | В                                   | TBM2                           | Timer 2B mode register 2                            |  |  |  |  |  |  |

|       |        |                                                   | С                                   | T2IC                           | Timer 2 interrupt control                           |  |  |  |  |  |  |

|       |        |                                                   | D                                   | T2PC                           | Timer 2 prescaler control                           |  |  |  |  |  |  |

|       |        |                                                   | Е                                   |                                |                                                     |  |  |  |  |  |  |

|       |        |                                                   | F                                   |                                |                                                     |  |  |  |  |  |  |

| A     | EMS    |                                                   | ı                                   | EEPROM                         | status register                                     |  |  |  |  |  |  |

| В     | ESUB   | Subport for EEPROM                                |                                     |                                | Row 0 – Row F                                       |  |  |  |  |  |  |

| С     | CSUB   | Subport for watchdog, timer 1, interrupt          | Sub-<br>address                     | Name                           | Register                                            |  |  |  |  |  |  |

|       |        | masks, and clock                                  | 0                                   | WDC                            | Watchdog control register                           |  |  |  |  |  |  |

|       |        | generator                                         | 1                                   | CWD                            | Clear watchdog counter                              |  |  |  |  |  |  |

|       |        |                                                   | 2                                   | CSC                            | Clock status/control register                       |  |  |  |  |  |  |

|       |        |                                                   | 3                                   |                                |                                                     |  |  |  |  |  |  |

|       |        |                                                   | 4                                   | T1C                            | Timer 1 control register                            |  |  |  |  |  |  |

|       |        |                                                   | 5                                   | IMR1                           | Interrupt mask register 1                           |  |  |  |  |  |  |

|       |        |                                                   | 6                                   | IMR2                           | Interrupt mask register 2                           |  |  |  |  |  |  |

|       |        |                                                   | 7-F                                 |                                |                                                     |  |  |  |  |  |  |

| D     |        |                                                   |                                     |                                |                                                     |  |  |  |  |  |  |

| Е     |        |                                                   |                                     |                                |                                                     |  |  |  |  |  |  |

| F     |        |                                                   |                                     |                                |                                                     |  |  |  |  |  |  |

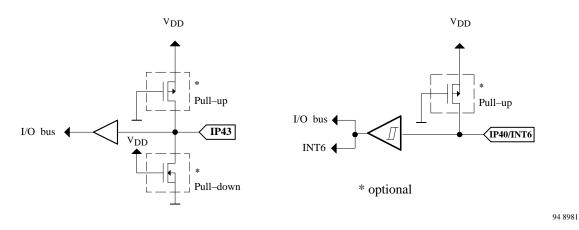

## **2.1.1** Input Port 4

Port 4 is the input port for the pins IP40, IP43, TA and TB. IP40 is also the interrupt input for INT6, and TA and TB are normally used for timer I/O functions.

|              | Bit 3 | Bit 2   | Bit 1   | Bit 0     |

|--------------|-------|---------|---------|-----------|

| Input port 4 | IP43  | TB/IP42 | TA/IP41 | IP40/INT6 |

Figure 11. Input port IP40, IP43

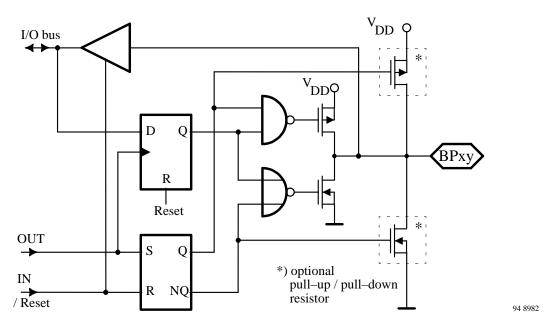

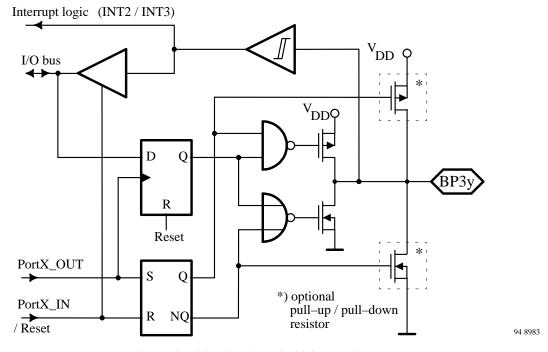

#### 2.1.2 Bidirectional Ports

Ports 0, 1, 2 and 3 are bidirectional 4-bit wide ports and may be used for data input or output. The data direction is programmable for a complete port only. The port is switched to output with an OUT-instruction and to input with an IN-instruction. The data written to a port will be stored into the output latches and appears immediately after the OUT-instruction at the port pin. After RESET all output latches are set to Fh and the ports are switched to input mode.

**Note:** Care must be taken when switching bidirectional ports from output to input. The capacitive load at this port may cause the data read to be the same as the last data written to this port. To avoid this, when switching the direction one of the following approaches should be used.

- Use two IN-instructions and DROP the first data nibble read. The first IN switches the port from output to input, DROP removes the first invalid nibble and the second IN reads the valid nibble.

- Use an OUT-instruction followed by an IN-instruction. With the OUT-instruction the capacitive load is charged or discharged depending on the optional pull-up/pull-down configuration. Write a "1" for pins with pull-up resistors and a "0" for pins with pull-down resistors.

Figure 12. Bidirectional port

Figure 13. Bidirectional port 3 with interrupt input

## 2.1.3 External Interrupt Inputs

The pins IP40 and BP30 – BP33 can be used as external interrupt inputs. IP40 is used for INT6, BP32 and BP33 are used for INT3, and BP30 and BP31 are used for INT2. Pin IP40 is also used as an input port and BP30 – BP33 as

a bidirectional port (see figure 11). Each of these external interrupt sources can be enabled or disabled with individually interrupt mask bits. A negative transition at one of these inputs requests an interrupt, when the corresponding mask bit is set. The interrupt masks are placed in the subport registers IMR1 and IMR2 of port CSUB.

Figure 14. External interrupt inputs

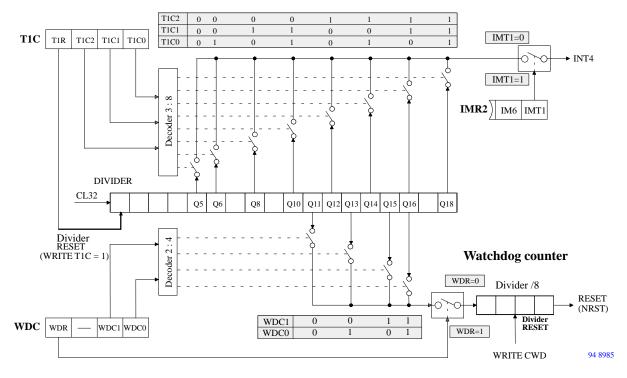

## 2.2 Timer 1

Timer 1 is an interval timer for generating interrupts. Additional to the timer can be used as watchdog timer. The timer consists of a programmable 18 stage divider which is supplied with a 32-kHz clock and a 3-bit counter for the watchdog function (see figure 15). The time interval for a timer 1 interrupt (INT4) can be programmed with the timer control register from 1 ms up to 8.0 s. The timer 1 interrupt is maskable with the IMT1 bit.

The time interval for a watchdog reset can be programmed with the watchdog control register for 0.5, 2.0, 8.0 or 16.0 s. When the watchdog is active (WDR = 1, T1R = 1) the controller is reset with the overflow of the 3-bit watchdog counter. The application software has to ensure that the watchdog counter is reset by a write access to the CWD port before it overflows. Because the watchdog timer is supplied by the interval timer it is necessary that timer 1 is set active (T1R = 1).

Figure 15. Timer 1

#### Timer 1 register

The registers of Timer 1 are I/O-mapped. They are subport register of port CSUB the access is made by extended I/O operations. The interval timer is controlled by the prescaler control register T1C. The interrupt mask IMT1 is placed in the interrupt mask register IMR2. The watchdog timer is controlled by the watchdog control register WDC and port CWD. A write access to CWD resets the watchdog counter.

## 2.2.1 T1C – Timer 1 Control Register

Address: 'C'h Subaddress 4

| TIC | T1R   | T1C2 | T1C1 | T1C0 | Reset value: 0000b |

|-----|-------|------|------|------|--------------------|

|     | Bit 3 | 2    | 1    | 0    |                    |

T1R Timer 1 reset

T1R = 1 resets the interval timer

T1C2 Timer 1 control bit 2

T1C1 Timer 1 control bit 1

T1C0 Timer 1 control bit 0

This both bits select the time interval for a Timer 1 interrupt.

| T1C2 | T1C1 | T1C0 | Divider | Time Interval |

|------|------|------|---------|---------------|

| 0    | 0    | 0    | 32      | 0.9765625 ms  |

| 0    | 0    | 1    | 64      | 1.953125 ms   |

| 0    | 1    | 0    | 256     | 7.8125 ms     |

| 0    | 1    | 1    | 1024    | 31.25 ms      |

| 1    | 0    | 0    | 4096    | 125 ms        |

| 1    | 0    | 1    | 16384   | 500 ms        |

| 1    | 1    | 0    | 65536   | 2 s           |

| 1    | 1    | 1    | 262144  | 8 s           |

## 2.2.2 WDC – Watchdog Control Register

Address: 'C'h Subaddress 0

| IIIDG | Bit 3 | 2 | 1    | 0    |                    |

|-------|-------|---|------|------|--------------------|

| WDC   | WDR   |   | WDM1 | WDM0 | Reset value: 0x00b |

WDR Watchdog run

WDR = 0 the watchdog counter is inactive and reset

WDR = 1 the watchdog counter is active and able to generate a reset when Timer 1 is running

WDC1 Watchdog mode 1WDC0 Watchdog mode 0

This both bits control the time interval for the watchdog reset.

#### **TELEFUNKEN Semiconductors**

| WDM 1 | WDM 0 | Divider | Delay time to Reset (s) |

|-------|-------|---------|-------------------------|

| 0     | 0     | 2048    | 0.5                     |

| 0     | 1     | 8192    | 2                       |

| 1     | 0     | 32768   | 8                       |

| 1     | 1     | 524288  | 16                      |

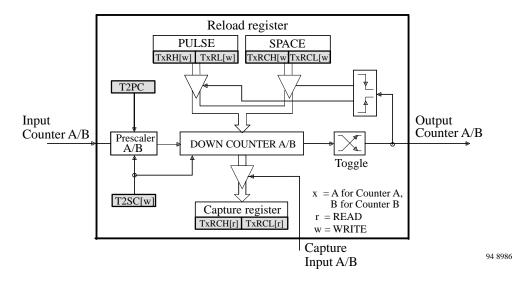

## 2.3 Timer 2

Timer 2 consists of the two timer/counter blocks Timer A and Timer B. Each block has one 8-bit downcounter and a programmable prescaler. The clock inputs can be programmed to count the system clocks, Timer A clocks or external clocks. The maximum clock rate for external clocks is the half system clock frequency (SYSCL/2). Each counter has a reload register for the pulse time and a reload register for the space time. Every counter underflow toggles the output and reloads the downcounter alternately from the pulse reload register or from the space reload register. This allows the generation of any duty cycles.

Addition both counters have a capture mode. In this mode an external signal or the Counter B output causes the current counter value to be captured into the corresponding capture register.

The timer has two I/O pins, TA for Timer A and TB for Timer B. Used as output the pins have a high level during the pulse time and a low level during the space time of the timer. As input the pins are used for the external counter clock or the capture signal. The inputs have a programmable edge detection to select the active edge of an external clock or capture signal.

Interrupts can be generated when a counter underflow or a capture event occurs. The interrupt function for timer 2 can be programmed with the interrupt control register. Both counter blocks share one interrupt vector (INT5).

#### **Timer 2 Modes**

There are various timer/counter modes for both blocks of Timer 2. They can be used separately or combined. The timer modes can be programmed with the timer control and mode registers.

#### **Single Timer Modes**

#### • 8-bit timer

Counter A/B is supplied by the system clock and is used to generate timer interrupts.

#### • Pulse width modulation

Counter A/B is supplied by the system clock. The

TA/TB pin is used as counter output. The duty cycle can be programmed with the pulse and space reload register.

## • Capture mode

Counter A/B is supplied by the system clock. The TA/TB pin is used as input. An external signal at the input causes the current counter value to be captured into the capture register.

#### Event counter

Counter A/B counts external clocks at the TA/TB pin. The capture register contains the current counter value and can be read.

#### **Combined Timer Modes**

#### • 16-bit timer

Counter A is supplied system clock and its output is coupled with the input of Counter B. In this mode the counter is used to generate timer interrupts.

#### • 16 bit capture mode

Counter A is supplied with the system clock and Counter B with the output of Counter A. An external signal at the TA pin causes the current counter value will be captured into the capture registers.

#### • 16-bit event counter

The output of Counter A is coupled with the input of Counter B to count external clocks at TA. The capture register of both counters contain the current counter values.

#### Burst generator

Counter A is supplied the system clock and its output is coupled with the input of Counter B. The output of Counter B controls the output signal of Counter A at the TA pin. The TA output is enabled during the pulse and disabled during the space of Counter B.

#### • Event counter with time gate

Counter A counts the clocks at the TA pin and Counter B is supplied with the system clock. Each underflow of Counter B causes the counter value of Counter A to be captured into its capture register.

#### **Timer 2 Register**

All timer register are I/O mapped. The access to the Timer 2 status control register (T2SC) can be done with a direct I/O operation to T2SC. The status is read with an IN operation and a command to control the timer is written with an OUT operation. The remaining registers of Timer 2 are subport registers of port T2SUB. The access to those

registers needs an extended I/O operation. The timer function can be configured with the mode registers TAM1, TAM2, TBM1, TBM2 and the interrupt control register T2IC. The timing depends on the contents of the prescaler control register T2PC and the reload registers. The capture registers are used to read the counter value.

Figure 16. Timer 2

Figure 17. Counter A/B

#### **TELEFUNKEN Semiconductors**

## 2.3.1 Timer 2 Status/Control Register (T2SC)

Address: 8

Control register

Bit 3

2

1

0

Write (T2SC)

TBM

TAM

TBR

TAR

Reset value: 0000b

Status register

Read (T2SC) TBSU TBPC TASU TAPC Reset value: 0000b

**TAM, TAR:** Timer A control bits to start or stop Timer A.

**TBM**, **TBR**: Timer B control bits to start or stop Timer B.

| TBM | TAM | TBR | TAR | Timer 2 Commands |

|-----|-----|-----|-----|------------------|

| 1   | 0   | X   | 0   | STOP_A           |

| 1   | 0   | X   | 1   | RUN_A            |

| 0   | 1   | 0   | X   | STOP_B           |

| 0   | 1   | 1   | X   | RUN_B            |

| 0   | 0   | 0   | 0   | STOP_AB          |

| 0   | 0   | 1   | 1   | RUN_AB           |

| 0   | 0   | 0   | 1   | RUN_A-STOP_B     |

| 0   | 0   | 1   | 0   | STOP_A-RUN_B     |

| 1   | 1   | Х   | X   | NOP              |

A STOP command resets the prescaler and counter.

A RUN command starts the counter with the next clock taking the value from the pulse reload register.

**TBSU:** Timer B end of space/underflow status bit.

When  $BCE^* = 0$  this bit will be set at the end of space time of Counter B. When BCE = 1 this bit will be set with every Counter B underflow.

**TBPC:** Timer B end of pulse/capture status bit.

When BCE = 0 this bit will be set at the end of pulse time of Counter B. When BCE = 1 this bit will be set when a capture event for Counter B occurs.

**TASU:** Timer A end of space/underflow status bit.

When  $ACE^* = 0$  this bit will be set at the end of space time of Counter A.

When ACE = 1 this bit will be set with each Counter A underflow.

**TAPC:** Timer A end of pulse/capture status bit.

When ACE = 0 this bit will be set at the end of pulse time of Counter A. When ACE = 1 this bit will be set when a capture event for Counter A occurs.

\*) ACE and BCE are the capture enable control bits in the timer mode registers TAM2 and TBM2.

The status bits TASU, TAPC, TBSU, TBPC will be reset after a READ access to T2SC!

## 2.3.2 Timer 2 Subport (T2SUB)

Address: 9

Table 7. Timer 2 subports

| Subaddr. | Name                             | Meaning                   |            | Bit 3       | Bit 2 | Bit 1  | Bit 0 |  |

|----------|----------------------------------|---------------------------|------------|-------------|-------|--------|-------|--|

| 0        | 0 TARCH [w]* Timer A reload high |                           |            | High-nibble |       |        |       |  |

|          | TARCH [r]*                       | Timer A capture high      |            |             |       |        |       |  |

| 1        | TARCL [w]*                       | Timer A reload low        |            |             | Low-  | nibble |       |  |

|          | TARCL [r]*                       | Timer A capture low       |            |             |       |        |       |  |

| 2        | TARH                             | Timer A reload high       |            |             | High- | nibble |       |  |

| 3        | TARL                             | Timer A reload low        |            |             | Low-1 | nibble |       |  |

| 4        | TBRCH [w]*                       | Timer B reload high       |            |             | High- | nibble |       |  |

|          | TBRCH [r]*                       | Timer B capture high      |            |             |       |        |       |  |

| 5        | TBRCL [w]*                       | Timer B reload low        | Low-nibble |             |       |        |       |  |

|          | TBRCL [r]*                       | Timer B capture low       |            |             |       |        |       |  |

| 6        | TBRH                             | Timer B reload high       |            | High-nibble |       |        |       |  |

| 7        | TBRL                             | Timer B reload low        |            | Low-nibble  |       |        |       |  |

| 8        | TAM1                             | Timer A mode register 1   |            |             | AGB   | ACS    | AOE   |  |

| 9        | TAM2                             | Timer A mode register 2   |            | ACB         | ACE   | AE1    | AE0   |  |

| A        | TBM1                             | Timer B mode register 1   |            |             | BCS1  | BCS0   | BOE   |  |

| В        | TBM2 Timer B mode register 2     |                           |            | BCA         | BCE   | BE1    | BE0   |  |

| C        | T2IC Timer 2 interrupt control   |                           |            | IMBS        | IMBP  | IMAS   | IMAP  |  |

| D        | T2PC                             | Timer 2 prescaler control |            | BPC1        | BPC0  | APC1   | APC0  |  |

| Е        |                                  |                           |            |             |       |        |       |  |

| F        |                                  |                           |            |             |       |        |       |  |

<sup>\* [</sup>w] write only, [r] read only

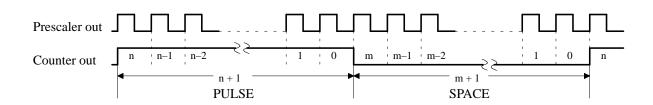

## 2.3.3 Timer 2 Reload Register

The 8-bit wide reload registers of Timer A and B are used to program the pulse and space width of the counter output signal.

The first clock after a start command loads the downcounter with the value (n) from the pulse reload register and sets the counter output to 1. The downcounter decrements with each following clock and each underflow reloads alternately the value (m) from the space reload register or the value (n) from the pulse reload register and toggles the counter output.

The pulse and space width can be calculated as following:

Pulse time: Pulse = (n+1) x prescaler clocks

Spacetime: Space = (m+1) x prescaler clocks

$0 \le m, n \le 255$

#### **Timer 2 Space Reload Register**

The space reload register of Timer 2 is programmed by two write accesses to the subport addresses TARCH and TARCL or TBRCH and TBRCL of the Timer 2 subport T2SUB. The value (m) in the space reload register determines the space width. At the end of pulse the downcounter reloads the 8-bit value from the space reload register with the next clock of the prescaler output.

Space width: Space = (m+1) prescaler clocks  $0 \le m \le 255$

#### **Timer 2 Pulse Reload Register**

The pulse reload register of Timer 2 is programmed by two write accesses to the subport addresses TERH and TARL or TBRH and TBRL of the Timer 2 subport T2SUB. The value (n) in the pulse reload register determines the space width. At the end of space the downcounter reloads the 8-bit value from the pulse reload register with the next clock of the prescaler output.

Pulse width: Pulse = (n+1) prescaler clocks  $0 \le n \le 255$

## 2.3.4 Timer 2 Capture Register

The capture register is used to capture the current down-counter value when a capture event occurs. The value is kept in the capture register until the next capture event and can be read independent of the state of the down-counter. The capture events are programmable with the timer mode registers TAM2 and TBM2.

The capture registers are also used to read the counter value when the external capture mode is disabled. In this case the 8-bit counter value is transferred into the capture register by reading the high nibble TARCH or TBRCH. If the 16-bit event counter mode is enabled the complete 16-bit value is captured by reading first the high nibble TARCH of Timer A. This mechanism ensures the coherence of the counter high and low nibble during the read access.

## 2.3.5 Timer A Mode Register 1 (TAM1)

Address: 9-Subaddress: 8

Bit 3 2 1 0

TAM1 — AGB ACS AOE Reset value: 0000b

**AGB** Counter **A** output gated by Counter **B** output

AGB = 1 enables the burst generation mode. The output of Timer A is enabled during the pulse time of the Counter B and disabled (TA= 0) during the space time of the Counter B.

**ACS** Counter **A** clock select

This bit selects the source of the Counter A clock. When ACS = 0 the timer is supplied with internal SYSCL. When ACS = 1 the timer is supplied with an external clock on TA pin.

**AOE** Timer **A** output enable

AOE = 0 disables the counter output TA. AOE = 1 enables the counter output TA.

## M48C260

**TELEFUNKEN Semiconductors**

## 2.3.6 Timer A Mode Register 2 (TAM2)

Address: 9 – Subaddress: 9

Bit 3 2 1 0

TAM2 ACB ACE AE1 AE0

Reset Value: 0000b

**ACB** Timer **A** captured by Timer **B**

Selects the capture source for Timer A. When ACB = 0 the signal at the TA pin is used to generate a capture event. When ACB = 1 each transition at the Counter B output is used to generate a capture event for Timer A.

**ACE** Timer **A** capture enable

ACE = 1 enables the capture mode for Counter A. The occurrence of a capture event causes that the current downcounter value is loaded into the capture register.

AE1 Timer A edge select bit 1

AE0 Timer A edge select bit 0

Whit these bits the active edge for the counter clocks and capture signal is selected.

| AE1 | AE0 | Active Edge for Counter Clock/Capture Events                             |  |

|-----|-----|--------------------------------------------------------------------------|--|

| 0   | 0   | positive edge at TA pin                                                  |  |

| 0   | 1   | negative edge at TA pin                                                  |  |

| 1   | 0   | first positive edge after timer start and then each transition at TA pin |  |

| 1   | 1   | first negative edge after timer start and then each transition at TA pin |  |

## 2.3.7 Timer B Mode Register 1 (TBM1)

Address: 9 – Subaddress: Ah

Bit 3 2 1 0

TBM1 — BCS1 BCS0 BOE Reset value: 0000b

BCS1 Timer B clock select bit 1

BCS0 Timer B clock select bit 0

These bits select the source of Counter B clock.

| BCS1 | BCS0 | Counter B Input Signal      |

|------|------|-----------------------------|

| 0    | 0    | System clock (SYSCL)        |

| 1    | 0    | Output signal of Counter A  |

| X    | 1    | External input signal at TB |

**BOE** Timer **B** output enable

BOE = 0 disables the counter output TB. BOE = 1 enables the counter output TB.

## **TELEFUNKEN Semiconductors**

## 2.3.8 Timer B Mode Register 2 (TBM2)

Address: 9 – Subaddress: Bh

Reset value: 0000b

Bit 3 2 1 0

TBM2 BCA BCE BE1 BE0

**BCA** Timer B is captured with Timer A capture signal. With BCA = 1 the external capture signal for

Timer A is used to capture Timer B simultaneously with Timer A.

Note: It is possible to capture Counter B by a read access to TARCH

**BCE** Timer **B** capture enable

BCE = 1 enables the capture mode for Counter B. A capture event loads the current downcounter

value into the capture register.

BE1 Timer B edge select bit 1

**BE0** Timer **A** edge select bit **0**

With these bits the active edge for the counter clocks and capture signal is selected.

| BE1 | BE0 | Active Edge for Clock/Capture Events                                     |

|-----|-----|--------------------------------------------------------------------------|

| 0   | 0   | positive edge on TB pin                                                  |

| 0   | 1   | negative edge on TB pin                                                  |

| 1   | 0   | first positive edge after start timer and then each transition on TB pin |

| 1   | 1   | first negative edge after start timer and then each transition on TB pin |

## 2.3.9 Timer 2 Prescaler Control Register (T2PC)

Address: 9 – Subaddress: Dh

Bit 3 2 1 0

T2PC BPC1 BPC0 APC1 APC0 Reset Value: 0000b

BPC1 Timer B prescaler control bit 1

BPC0 Timer B prescaler control bit 0

These bits determine the divider for the prescaler of Timer B.

APC1 Timer A prescaler control bit 1

APC0 Timer A prescaler control bit 0

These bits determine the divider for the prescaler of Timer A.

| BPC1/APC1 | BPC0/APC0 | Divider |

|-----------|-----------|---------|

| 0         | 0         | 1       |

| 0         | 1         | 4       |

| 1         | 0         | 16      |

| 1         | 1         | 64      |

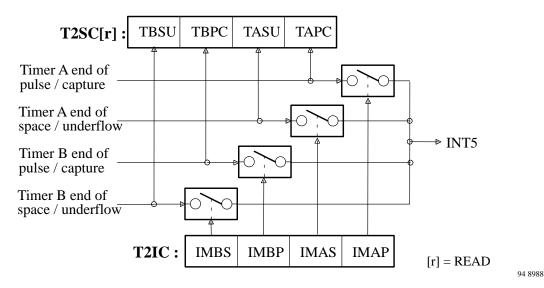

## 2.3.10 Timer 2 Interrupt Control Register (T2IC)

Address: 9 - Subaddress: Ch

|      | Bit 3 | 2    | 1    | 0    |                    |

|------|-------|------|------|------|--------------------|

| T2IC | IMBS  | IMBP | IMAS | IMAP | Reset value: 0000b |

IMBS Interrupt mask Timer B end of space/underflow

IMBS = 1 enables an INT5 interrupt, if BCE\* = 0 at the end of space of Counter B,

or if BCE = 1 at each Counter B underflow.

**IMBP** Interrupt mask Timer B end of pulse/capture

IMBP = 1 enables an INT5 interrupt, if BCE = 0 at the end of pulse of Counter B,

or if BCE = 1 with a capture event for Counter B.

**IMAS** Interrupt mask Timer A end of space/underflow

IMAS = 1 enables an INT5 interrupt, if  $ACE^* = 0$  at the end of space of Counter A,

or if ACE = 1 at each Counter A underflow.

IMAP Interrupt mask Timer A end of pulse/capture

IMAP = 1 enables an INT5 interrupt, if ACE = 0 at the end of pulse of Counter A,

or if ACE = 1 with a capture event for Counter A.

Each interrupt source can be enabled or disabled individually by setting the corresponding maskbit.

\*) ACE and BCE are the capture enable control bits in the timer mode registers TAM2 and TBM2.

Figure 18. Timer 2 interrupt mask register

94 8989

# TEMIC

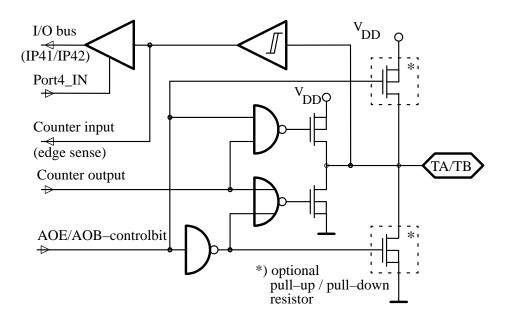

## **2.3.11** Timer I/O (TA/TB)

The timer I/O pins TA and TB are used as input for the external clock or capture signal and as output for the counter. The mode is controlled with AOE and BOE control bit. When AOE/BOE = 0 the pin is switched to

input mode, when AOE/BOE = 1 the pin is switched to output mode. The pins also can be read with an IN-instruction via port 4 (TA with IP41 and TB with IP42).

Figure 19. Timer I/O (TA/TB)

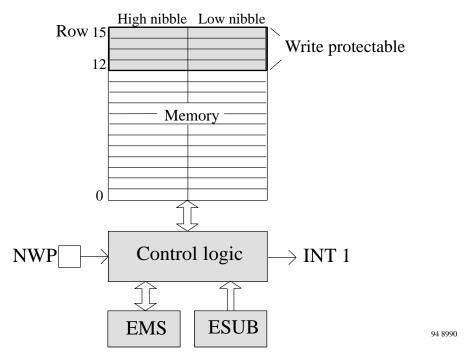

### 2.4 EEPROM

The EEPROM of the M48C260 is 128 bit wide and organized as an array of 16\*8-bit. The EEPROM rows are I/O mapped and are subports of port ESUB. The access to any 8-bit row of the EEPROM is done by an extended 8-bit

I/O operation or by special postincrement access. The EEPROM rows 12 to 15 can be write protected by hardware and software.

#### **EEPROM SubPort (ESUB)**

Address: Bh - Subaddress: 0-Fh

Figure 20. EEPROM

### **Read operation**

A read operation needs an OUT- and two IN-instructions to port ESUB. First the the OUT operation writes the row

address. The following two IN-instructions read the high nibble and then the low nibble of the addressed row.

### qFORTH example:

| Row address | ESUB OUT | (          | <u>—</u> )            |

|-------------|----------|------------|-----------------------|

|             | EPSUB IN | (          | —Data_High)           |

|             | EPSUB IN | (Data_High | — Data_High Data_Low) |

#### Write operation

A write operation needs three OUT-instructions to port ESUB. The first operation writes the row address. The following two OUT-instructions write the low nibble and then the high nibble to the addressed row. After reset, rows 12 to 15 are write protected. To enable write operations to these rows the write enable bit (EWE) must be set. In all cases write accesses to these rows are disabled when pin NWP is low.

#### qFORTH example:

| Row address | ESUB OUT  | (Data_High Data_Low | — Data_High Data_Low) |

|-------------|-----------|---------------------|-----------------------|

|             | EPSUB OUT | (Data_High Data_Low | —Data_High)           |

|             | EPSUB OUT | (Data_High          | —)                    |

#### **TELEFUNKEN Semiconductors**

The internal EEPROM write cycle needs about 16 ms. During this cycle the EEPROM ready bit is reset (EPR = 0). After the data high nibble is written to the port ESUB the internal write cycle is started. During the internal write cycle (while EPR = 0), only read and write accesses to the EMS register are possible. All other EEPROM accesses have no effect.

#### **Postincrement operations**

The postincrement mode supports a fast access to consecutive EEPROM rows. A postincrement access is started by setting the EPI bit in the EEPROM mode register (EMS) followed by writing the row start address to port ESUB. After that the read or write operations to the consecutive EEPROM area, beginning at the start address, need only two IN- or OUT-instructions to read or write the data. The row address is incremented automatically after each complete row access (2 nibbles). A write access to the EEPROM mode register (EMS) terminates the postincrement mode.

In the postincrement mode, it is not possible to change from read to write operations or vice versa before the current postincrement operation is finished.

### Write ready interrupt (INT1)

At the end of the internal write cycle an interrupt is generated when the interrupt mask bit IMEP in the EEPROM mode register EMS is set. With this interrupt, successive write operations can be executed interrupt controlled within the INT1 interrupt service routine.

Address: Ah

#### 2.4.1 **EEPROM Mode/Status Register (EMS)**

| Mode register   | Bit 3 | 2   | 1   | 0    |                    |

|-----------------|-------|-----|-----|------|--------------------|

| Write (EMS)     |       | EWE | EPI | IMEP | Reset value: 0000b |

| Status register |       |     |     |      |                    |

| Read (EMS)      |       |     |     | EPR  | Reset value: xxx1b |

**EWE** EEPROM write enable bit

EWE = 0 disables write accesses to rows 12-15

EWE = 1 enables write accesses to rows 12-15 when the NWP pin is high

**EPI** EEPROM postincrement mode enable

EPI = 1 activates a postincrement access after the next row address is written to port ESUB

**IMEP** Interrupt mask for EEPROM write ready interrupt

When IMEP is set an INT1 is generated with the end of the internal EEPROM write cycle

**EPR** EEPROM ready status flag

EPR = 0 indicates that the EEPROM is not ready for read or write operations

(an internal write cycle is executed)

EPR = 1 indicates that the EEPROM is ready for read and write operations

After a write access to the EMS-Register postincrement operations are terminated and any incomplete EEPROM read and write sequence must be started again!

## 3 Appendix

## 3.1 Emulation

For emulation all MARC4 controllers have a special emulation mode. It is activated by setting the TE pin to logic HIGH level during reset. In this mode the internal CPU core is inactive and the I/O buses are available via port 0 and port 1 to allow the emulator the access to the on-chip peripherals. The emulator contains a special emulation CPU with a MARC4 core and additional breakpoint logic and takes over the core function. The basic function of the emulator is to evaluate the customer's program and hardware in real time. Thus permits the analysation of any timing, hardware or software problems the simulation of the application. For more informations about emulation see "Emulator Manual".

# 3.2 Programming the EEPROM Program Memory

Programming the 4K × 8-bit EEPROM program memory is done using a special PC–controlled programming device. Details on use of this device and the corresponding software are given in the Programming Device User Manual.

To start programming the data memory, the micro-controller is switched to a special I/O mode, where the core and all peripherals are set inactive and the two I/O buses are available via port 0 (data) and port 1 (control). Then the customer application data is transfered to the controller vio port 0 in blocks of 64 nibble size. Programming is started automatically after each block. The programming high voltage is generated on chip.

After programming the memory a verify run is started, where the just written data is read out and compared bit by bit to the original source file. This ensures that the contents of the ROM is error free.

#### 3.3 MARC4 Instruction Set

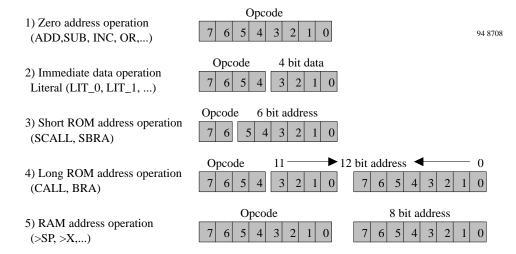

The MARC4 instruction set is optimized for the high level programming language qFORTH. A lot of MARC4 instructions are qFORTH words. This enables the compiler to generate fast and compact program code. The MARC4 is a zero address machine with a compact and efficient instruction code. Most of the instructions are

single byte instructions. This operations are performed and no source or destination address information. Only BRANCH, CALL and RAM access instructions need address informations and a length of two bytes for long address operations. In all there are five types of instruction formats with a length of one and two bytes.

Zero address operations like arithmetical, logical, shift and rotate operations are performed with data placed on the top of expression stack (TOS and TOS-1). Also I/O- and stack operations are single byte zero address operations and are performed with the top expression stack location.

A literal is a 4-bit constant value which is placed on the data stack. In the MARC4 native code they are represented as LIT\_<value>, where <value> is the hexadecimal representation from 0 to 15 (0...F). This range is a result of the MARC4's 4-bit data width. The 6-bit short address and the 12-bit long address formats are both used to address the byte-wide ROM via CALL and conditional branch instructions. This results in a ROM address space of up to 4K\*8-bit words.

The MARC4 instruction includes both short and long call instructions as well as conditional branch instructions. On execution the address part of the instructions word are directly loaded into the program counter. Long call and branch instructions can jump anywhere within the program memory area..The lower six bits from the short call (SCALL) and short branch (SBRA) instruction are handled in different way. The six bit SCALL address is multiplied by three and then loaded into the PC. This allows calls within the zero page (000 to 1FFh). The six bit SBRA address is loaded immediately into the lower six bits of the PC. This allows jumps within the 64 byte segment addressed by the upper six bits of the PC.

The CALL and SCALL instructions write the incremented program counter contents to the return stack. This address is loaded back to the PC when the associated EXIT or RTI instruction is encountered. The long RAM address format is used by the four 8-bit RAM address registers which can be pre-increment, post-decrement or loaded directly from the MARC4's internal bus. This results in a direct accessible RAM address space of up to  $256 \times 4$ -bit.

## **TELEFUNKEN Semiconductors**

Figure 21. MARC4 opcode formats

#### **MARC4 Instruction Set Overview** 3.3.1

| Mnemonic | Description                            | Cycles/<br>Bytes |

|----------|----------------------------------------|------------------|

|          |                                        |                  |

| ADD      | Add                                    | 1/1              |